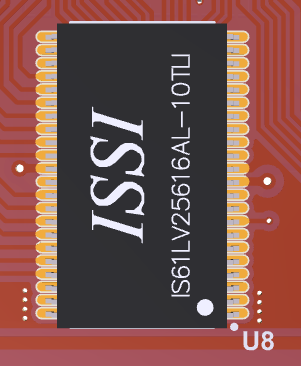

حافظه SRAM

سلام

در این پروژه ی نمونه، به منظور آشنایی با نحوه ی خواندن و نوشتن در SRAM، با یک SRAM Controller ساده اما کارآمد آشنا خواهیم شد که برگرفته از مثال ارائه شده در بخش 11.4.5 کتاب معروف “FPGA Prototyping by Verilog Examples” بوده که بر روی برد پازج-یک پورت شده است.

در این پروژه:

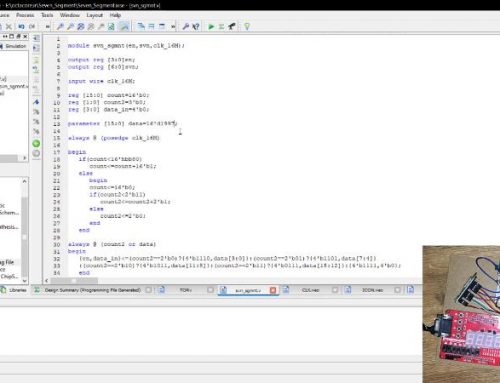

– ابتدا یک دنباله ی منظم از اعداد با ماکزیمم سرعت روی SRAM نوشته میشود.

– سپس محتوای SRAM با حداکثر سرعت خوانده شده و داده های بازخوانی شده با الگوی اصلی مقایسه شده و تعداد خطاهای احتمالی روی نمایشگر سون سگمت نمایش داده میشود.

– به منظور اطمینان از صحت تست، این امکان نیز وجود دارد که کاربر به مقادیر نوشته شده روی SRAM بصورت دستی خطا تزریق نماید و نتیجه ی آن را در تست ملاحظه نماید.

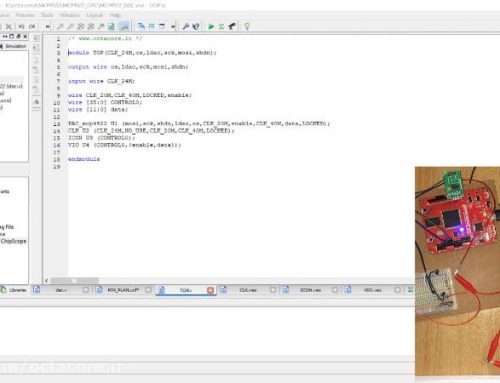

لازم به ذکر است جهت اعمال ورودی ها و مشاهده خروجی روی سگمنت در این پروژه از مگاوینگ LogiX-1 پازج استفاده شده است.

روند اجرای تست بر روی برد پازج-یک به همراه مگاوینگ LogiX-1 بدین صورت است:

0- مگاوینگ را روی برد نصب کرده و برد خود را با استفاده از فایل .bit ارئه شده در پوشه پروژه پیکره بندی کنید.

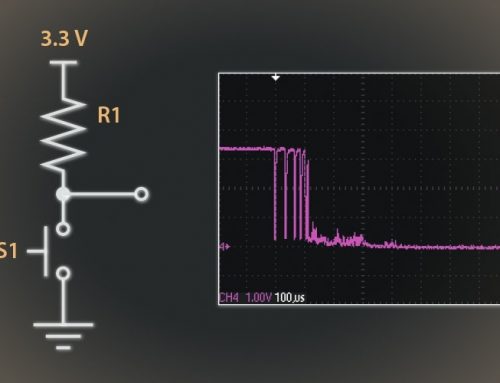

1- پس از اینکه FPGA برنامه ریزی شد، با فشردن کلید S1 روی مگاوینگ، مقادیر موجود روی SRAM خوانده شده و مورد ارزیابی میشوند. از آنجاییکه هنوز چیزی روی SRAM نوشته نشده است، انتظار داریم مقدار خطای بزرگی روی خروجی سون سگمنت نمایش داده شود.

2- با فشردن کلید S2 روی مگاوینگ، دنباله ای از مقادیر متوالی درون SRAM نوشته میشود.

3- اکنون بار دیگر کلید S1 را فشار دهید و نتیجه را مشاهده نمایید. انتظار میرود تعداد خطاهای نمایش داده شده روی سون سگمنت 0 باشد.

4- حال با تنظیم یک مقدار آدرس دلخواه روی دیپ سوئیچ و سپس فشردن کلید S3، یک مقدار اشتباه در آدرس مذکور درون SRAM نوشته میشود (تزریق خطا). این کار را چندین بار برای آدرس هایی متفاوت تکرار کنید. پس از هر بار تزریق خطا، با فشردن کلید S1 انتظار داریم تعداد خطاها یک عدد افزایش یافته باشد.

جهت اطلاع بیشتر در رابطه با جزئیات پروژه میتوانید به منبع اشاره شده در ابتدای این متن مراجعه فرمایید. بعلاوه در منبع مذکور راهکارهایی جهت بهینه سازی این طرح و افزایش سرعت خواندن/نوشتن تا 3 برابر طرح فعلی نیز ارائه گردیده که مطالعه آن به علاقمندان توصیه میگردد. امیدواریم با سایر منابع آموزش FPGA تهیه شده توسط گروه پازج همراه باشید