رفقای پازجی، سلام!

در این نوشته به بررسی چگونگی ایجاد یک ارتباط سریال ساده از نوع UART بین FPGA و PC خواهیم پرداخت. البته قبلا طی یک آموزش تصویری با نحوهی ایجاد یک ارتباط UART ساده با استفاده از پردازندهی MicroBlaze آشنا شدیم، اما از آنجایی که در بسیاری از کاربردها نیاز داریم تا ارتباط سریال را بدون استفاده از میکروبلیز داشته باشیم در این پروژهی نمونه به پیادهسازی یک ارتباط سریال UART بدون استفاده از MicroBlaze و در قالب چند ماژول سختافزاری ساده خواهیم پرداخت. لازم به ذکر است ارتباط UART بین کامپیوتر و FPGA در این پروژه از طریق تراشهی مبدل USB به UART موجود روی برد پازج-یک (تراشهی FT2232H) برقرار شده است.

از آنجایی که اصول اولیه ارتباط UART در اکثر مراجع آموزشی میکروکنترلرها ذکر شده و به احتمال زیاد اکثر شما با آن آشنا هستید از ذکر مقدمات و مبانی این ارتباط خودداری کرده و یک راست به سراغ اصل ماجرا میرویم! همچنین از آنجایی که هدف از ارائهی “طرحهای نمونه” (Sample Design) فراهم کردن یک الگوی آماده جهت بکارگیری در سایر پروژهها است، تنها به توضیح کلیات طرح و نحوهی استفاده از آن در پروژههای دیگر بسنده میکنیم و وارد جزئیات طراحی داخلی ماژولها نمیشویم.

توضیحات:

این طرح نمونه متشکل از یک ماژول گیرنده (uart_rx_fifo) و یک ماژول فرستنده (uart_tx_fifo) دادههای سریال است که توسط ماژول سومی به نام rx_to_tx تشکیل یک “حلقه برگردان” یا “loopback” را دادهاند؛ بدین معنی که دادههایی که از طرف PC ارسال شده و توسط ماژول گیرنده دریافت میشوند، بطور پیوسته توسط ماژول واسط rx_to_tx خوانده شده و به ماژول TX داده میشود تا به کامپیوتر برگردانده شود. تکنیک “حلقه برگردان” یک روش مرسوم جهت تست عملکرد لینکهای ارتباطی است که قبلا در طرح نمونهی “ارتباط USB با سرعت 8MB/s در حالت Asyncronous FIFO” نیز از آن استفاده کردیم.

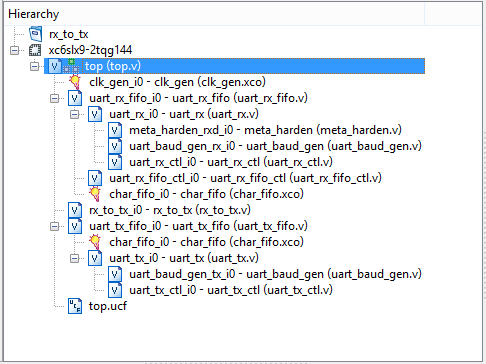

ساختار سلسله مراتبی طرح ما در شکل زیر نمایش داده شده است:

- ماژول clk_gen شامل یک کور PLL است که توسط CORE Generator موجود در ISE تولید شده است و وظیفهی آن تولید کلاک 40MHz مورد نیاز سایر ماژولها از روی کلاک 24MHz تامین شده توسط کریستال روی برد است.

- ماژول uart_rx_fifo وظیفهی دریافت دادههای ارسالی از جهان خارج (که در مثال ما یک PC است) و ذخیرهی آن درون یک FIFO با عمق 1K را دارد. برای خواندن اطلاعات ارسالی کافی است تا دیتای موجود در این FIFO را بخوانید. به همین سادگی، به همین خوشمزگی!

- ماژول uart_tx_fifo نیز مجهز به یک FIFO است که کاربر آن را با اطلاعات دلخواه خودش پر میکند و ماژول بطور پیوسته دادههای درون این FIFO را خوانده و به سمت کامپیوتر ارسال میکند. با این اوصاف کاربر عملا از درگیری با جزئیات ارتباط سریال معاف بوده و تنها کاری که بایستی انجام دهد خواندن و نوشتن اطلاعات از/به FIFO های RX و TX است.

- ماژول rx_to_tx نیز تنها به جهت تست عملکرد طرح است و قابلیت دیگری ندارد. بنابراین چنانچه قصد دارید تا این طرح نمونه را در پروژههای خود استفاده کنید، میتوانید این ماژول را حذف کنید.

توجه: بصورت پیشفرض ماژولهای فرستنده و گیرندهی UART موجود در این طرح همگی روی کلاک ورودی 40MHz و باود ریت 9600 تنظیم شدهاند. چنانچه بخواهید فرکانس پالس کلاک ورودی و یا baud rate را تغییر دهید، بایستی پارامترهای CLOCK_RATE و BAUD_RATE را در ماژولهای uart_rx_fifo و uart_tx_fifo تغییر دهید.

جهت تست این طرح نیز کافی است تا پس از اجرای پروژهی ISE ارائه شده در فایل پیوست و تولید فایل bit و پروگرام کردن آن روی برد پازج-یک، از طریق نرمافزاری مانند putty یک ارتباط سریال با برد برقرار کنید (چنانچه با نحوهی انجام این کار آشنایی ندارید به راهنمای کاربری برد پازج-یک مراجعه نمایید). چنانچه همه چیز به خوبی پیش رفته باشد، بایستی پس از تایپ هر کاراکتر در کنسول سریال، بلافاصله همان کاراکتر به شما برگشت داده شود.

امیدوارم این طرح نمونه به کارتان آمده باشد. درصورت علاقمندی به موضوعات پیرامون می توانید سایر مطالب مربوط به آموزش FPGA ما را نیز مطالعه نمایید

لطفا سوالات فنی خود در رابطه با این نوشته را در تاپیک مربوط به این نوشته در انجمن مطرح نمایید.

always@posedge باشید!

فایلهای پیوست:

فایلهای سورس و پروژهی ISE (دانلود)

سلام و خسته نباشید.

به نظر بنده و با توجه به اینکه این گروه قصد گسترش دادن مجموعه پازج رو داره، آموزش های شما به صورت تصویری و کلیپ باشه خیلی خیلی خیلی بهتره. اموزش های قبلی خیلی خوب بود. و اینکه از اونجا که برد پازج پورت سریال و حافظه جانبی SRAM هم دارد، بنظرم باید واسه یک بارم که شده اموزش تصویری برای این دو موضوع مهم قرار داده بشه(واسه همیشه دیگه). چون خیلی کاربرد دارن و اکثرا هم تو این موضوعات مشکل دارن.

علاوه بر این موارد در موقع فروش این برد اگه نرم افزار ISE اخرین ورژنش و همچنین نمونه کد های راه اندازی در جعبه برد قرار داشته باشه خیلی خیلی بهتره و مطمئا بازدهی گروه پازج رو بالا میره.

سلام

خیلی ممنون از پیشنهادتون

چشم. انشاءالله آموزش تصویری این دو مبحث به زودی در اختیار شما دوستان عزیز قرار داده خواهد شد.

در مورد نرمافزار ISE هم انشاءالله به زودی سی دی حاوی آخرین نسخهی ISE در فروشگاه قرار داده میشود.

با تشکر

سلام.ببخشید در سورس کدنون آیا از روش handshaking استفاده کردید؟ میشه راجع به این روش توضیح مختصری بدهید.

سلام. خیر، handshaking در این پروژه پیاده سازی نشده. نه بشکل نرم افزاری (Xon/Xoff) و نه به شکل سخت افزاری (که به سیگنالهای اضافی مثل RTS یا CTS نیاز هست).

بسیار بسیار عالی هم برد خوبی درست کردید هم آقای صادقی خوب توضیح دادن