دوستان عزیز پازجی سلام؛

از شما دوستان بابت تاخیر در ارائه مقالات آموزش FPGA پوزش می طلبیم. در روز های آینده سعی خواهد شد به بحث آموزش FPGA در سایت و انجمن بیشتر پرداخته شود.

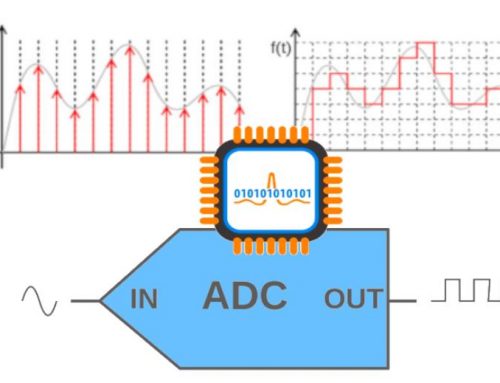

در این نوشته ابتدا به بررسی اجمالی تراشهی FT2232H و قابلیتهای ارتباطی آن پرداخته و در ادامه با ارائهی یک پروژهی کامل، یک ارتباط USB با نرخ 8MB/s بین FPGA موجود روی برد توسعهی پازج-1 و PC برقرار نموده و توسط تست loopback، میزان performance آن را مورد ارزیابی قرار میدهیم. سرعت این ارتباط بیش از 8MB/s است. بنابراین قبل از مطالعهی ادامهی مطلب، کمربندهای ایمنی را بسته، محکم به صندلی تکیه داده و خود را برای یک جهش صعودی با شیب ناملایم(!) آماده کنید!

مقدمه: در باب FT2232H و خواص آن…

احتمالا تابحال نام شرکت FTDI و محصولات آن به گوشتان خورده است. این شرکت گسترهی متنوعی از تراشههای مبدل USB به پروتکلهای متفاوت را تولید میکند که تراشهی FT232R از جمله معروفترین آنهاست که در بین اکثر کاربران شناخته شده است. اما تراشهی مورد بحث ما در این نوشته، عضو دیگری از خانواده تراشههای FT، یعنی تراشهی FT2232H است که قابلیتهای بسیار بیشتری نسبت به FT232R دارد. برخی از مهترین ویژگیهای شاخص این تراشه عبارتند از:

- مبدل USB به دو کانال مجزا (به نامهای A و B) با قابلیت پیکرهبندی هر کانال در یکی از مودهای UART، Synchronous FIFO، Asynchronous FIFO، Bit-Bang، MPSSE، Fast Serial، CPU-Style FIFO و Host Bus Emulation.

- پشتیبانی از استاندارد USB 2.0 در مودهای High Speed (480Mbps) و Full Speed(12Mbps).

- مبدل USB به Synchronous FIFO با سرعت حداکثر 40MB/s.

- مبدل USB به Asynchronous FIFO با سرعت حداکثر 10MB/s.

- پیاده سازی کامل پروتکل USB به صورت سختافزاری درون تراشه و عدم نیاز کاربر به درگیری با جزئیات این پروتکل.

در برد پازج-1 نیز از این تراشه بهره گرفته شده است: “کانال A” جهت پیادهسازی پروگرامر رو-برد و “کانال B” جهت ارتباط FPGA و PC در یکی از دو حالت UART یا Async FIFO. در ادامه به بررسی نحوهی برقراری ارتباط FPGA و PC در حالت Async FIFO خواهیم پرداخت.

گام صفرم: پیکرهبندی مجدد تراشهی FT2232H

کانال “B” ی تراشهی FT2232H روی برد پازج-1 بصورت پیشفرض روی حالت UART تنظیم شده است. به منظور ایجاد ارتباط Async FIFO ، قبل از هر چیز لازم است تا تراشه مجددا پیکرهبندی شود.

توجه داشته باشید از آنجایی که تنظیمات مدار پروگرامر نیز در همین تراشه ذخیره شده است، هر گونه اشتباه در اجرای این فاز میتواند در عملکرد پروگرامر روی برد اختلال ایجاد کند که در اینصورت تنها راه حل ارجاع برد به ما جهت برنامهریزی مجدد است! بنابراین این مرحله را دقیقا مطابق دستورالعملی که در ادامه آورده میشود انجام دهید.

جهت تغییر پیکرهبندی FT2232H از حالت UART به Async FIFO :

- برنامهی ftdi_change_mode را که در آرشیو پیوست قرار دارد اجرا نمایید.

- با اجرای برنامه پنجرهای مطابق شکل زیر باز میشود که از شما درخواست میکند حالت عملکرد تراشه را انتخاب نمایید. برای تغییر به حالت FIFO عدد 2 و در صورتی که قصد بازگشت به حالت UART را دارید عدد “1” را وارد نموده و Enter را بزنید.

- یک بار برد را از کامپیوتر جدا کرده و مجددا متصل نمایید.

اکنون تراشهی FT2232H برای عملکرد در مود Async FIFO آماده است.

گام یکم: برنامهی سمت FPGA:

توضیحات طرح سختافزاری:

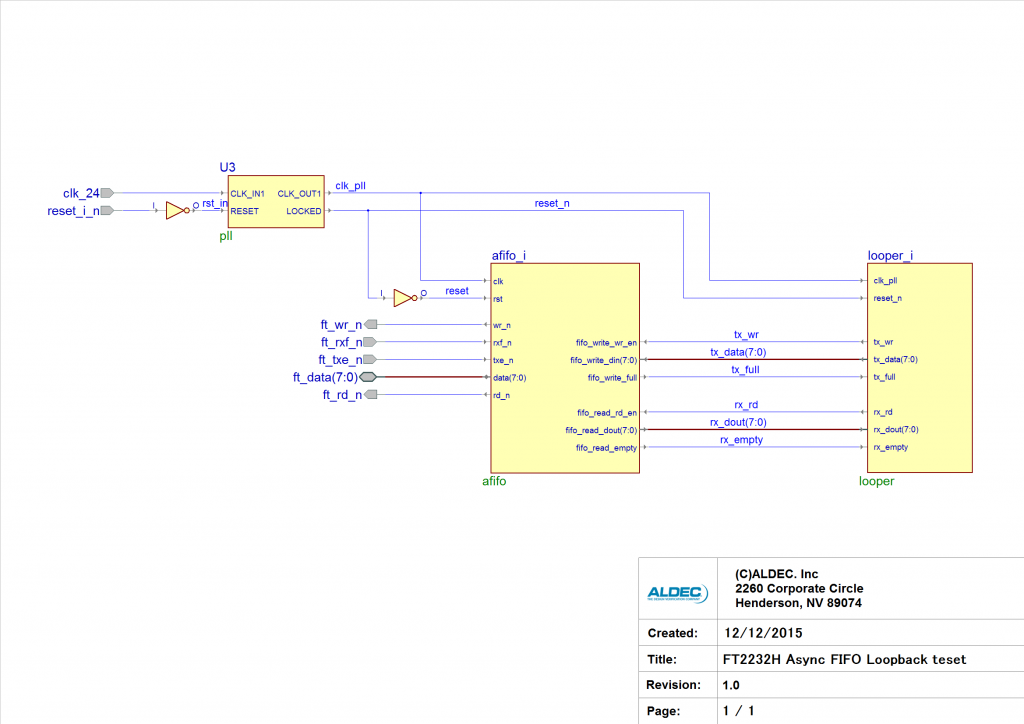

شماتیک top_module طرح سختافزاری سمت FPGA در شکل زیر نمایش داده شده است.

همانطور که مشاهده میشود طرح از سه ماژول اصلی تشکیل شده است که عملکرد آنها در ادامه به طور خلاصه تشریح میشود:

- ماژول pll جهت تولید سیگنالهای clock و reset از روی ورودی کلاک اسیلاتور 24 مگاهرتز و کلید ریست (USER_PB).

- ماژول afifo : این ماژول در واقع بعنوان مبدل اینترفیس Async FIFO به دو FIFO ی مجزا جهت دریافت و ارسال دیتا عمل میکند. همانطور که در شکل نیز مشخص است، در سمت چپ این ماژول سیگنالهای دیتا (ft_data) و handshaking (ft_wr_n، ft_rxf_n، ft_txe_n و ft_rd_n) قرار دارند که به تراشهی FT2232H متصل میشوند و در سمت راست آن، دو کانال FIFO ی مجزا به ظرفیت 4KB قرار گرفتهاند که کانال پایینی FIFO ی دریافت (RX) است که اطلاعات ارسالی از سمت PC به FPGA در آن ذخیره شده و کانال بالایی، FIFO ی ارسال (TX) است و دربرگیرندهی اطلاعاتی که قصد داریم از FPGA به سمت PC ارسال شود. در کنار خطوط دیتای هر FIFO، سیگنالهای خواندن/نوشتن و پرچم خالی/پر آن نیز قرار گرفته است که کاربر میتواند بر اساس آنها اقدام به خواندن و نوشتن از/به FIFO ی مورد نظر نماید.

- ماژول looper: این ماژول در واقع یک echo است که دیتای دریافت شده (ذخیره شده درون FIFOی RX) را برداشته و درون FIFO ی TX قرار میدهد تا دوباره به سمت کامپیوتر ارسال شوند. این کار تنها برای اطمینان از صحت عملکرد هر دو سمت ارتباط انجام شده است. در برنامهی تست سمت کامپیوتر، دیتای فرستاده شده و دریافت شده با یکدیگر مقایسه میشوند و در صورت عدم تطابق خطا محسوب میشود.

بارگذاری فایل پیکرهبندی روی FPGA:

پروژهی ISE مربوط به پیادهسازی این طرح روی برد پازج-1 درون پوشهی “/ISE” آرشیو پیوست قرار دارد. همچنین فایل .bit ساخته شده و آماده جهت پروگرام نیز در زیر پوشهی “Build/” درون پوشهی مذکور قرار داده شده است. برای پروگرم کردن FPGA کافی است تا با استفاده از نرمافزار Impact فایل .bit را روی FPGA پروگرام نمایید.

گام دوم: برنامهی سمت PC:

در سمت PC نیز دنباله ای از اعداد 8 بیتی متوالی (از 0x00 تا 0xFF) به صورت مرتب به سمت FPGA ارسال شده و سپس دادههای ارسال شده از سمت FPGA دریافت شده و با مقدار مورد انتظار مقایسه میشود (تست loopback). در صورتی که عدم تطابقی رخ دهد، مورد به عنوان خطا در نظر گرفته شده و یک واحد به مجموع خطاها اضافه میشود. در حین اجرای برنامه نیز زمان صرف شده جهت ارسال و دریافت اطلاعات نیز به دقت اندازهگیری شده که جهت محاسبهی نرخ تبادل اطلاعات به کار میرود. همچنین تعداد کل بایتهای رد و بدل شده، سرعت ارسال و دریافت و تعداد خطاها نیز به طور منظم در طول اجرای برنامه نمایش داده میشود (شکل زیر).

نتیجه گیری:

بار دیگر مراحل اجرای این پروژهی نمونه را به طور خلاصه مرور میکنیم:

- گام صفرم: قبل از هر چیز لازم است تا مود عملکرد آی سی FT2232H را که به صورت پیش فرض در حالت UART است را به حالت Asynchronous FIFO تغییر دهیم. برای این کار از برنامهی ftdi_change_mode که در آرشیو پیوست شده قرار دارد استفاده کنید. با اجرای فایل اجرایی داخل پوشه از طریق خط فرمان ویندوز و انتخاب حالت عملکرد FIFO، آی سی به صورت خودکار برنامه ریزی مجدد شده و در مود FIFO قرار میگیرد.

- در گام بعدی لازم است با اجرای نرم افزار ISE، پروژه ی ISE موجود در فایل پیوست را باز کرده و مراحل سنتز و پیادهسازی را اجرا نموده و در پایان فایل .bit تولید شده را روی FPGA ی موجود روی برد پازج-1 پروگرام کنید.

- در انتها با اجرای نرمافزار تست سمت PC، نتیجه را مشاهده نمایید.

امیدوارم از این آموزش لذت برده باشید. always@posedge باشید!

منابع جهت مطالعه بیشتر:

- FT2232H Datasheet

- D2XX_Programmer’s_Guide

- FT2232H Used in an FT245 Style Synchronous FIFO Mode

- Instructions On Including The FTD2xx DLL In A VS2008 Project

فایلهای پیوست:

دانلود (شامل نرمافزار ftdi_change_mode + پروژهی ISE (به همراه فایل .bit آماده) + پروژهی Visual Studio 2012 نرمافزار سمت PC)

با سلام.

یک سوال؟

الان فرض کنید که دیتا رو داریم از سمت Fpga ارسال میکنیم به سمت pc و باس مشغوله،حالا اگر کاربر بخواد یک دستوری رو بفرسته سمت Fpga این چجوری میشه؟

اصلا کلا عنگامی که دیتا رو بخوایم از سمت pc بدیم به fpga چکار باس بکنیم؟من الان از طرف fpga تونستم از روی دیتاشیت دیتا بدم و با terminal دیتا رو ببینم.

ولی در جهت مخالف نمیدونم چطور باید این کار رو انجام بدم..ممنون میشم راهنمایی کنید

سلام

اولا لازمه روی این نکته تاکید کنم که مود ارتباط USB ما در این حالت، به شکل UART نیست که شما در سمت کامپیوتر بتوانید با ترمینال دیتا بگیرید یا بفرستید. Terminal مال موقعی هست که مبدل USB مون در حالت UART قرار داشته باشه (که تبعا سرعت خیلی محدودتری هم داره)، در حالی که در این پروژه، مبدل USB در حالت FIFO (موازی) عمل میکنه و سمت PC باید خودتون برنامه نویسی کنید که یک نمونه برنامه ش در این پروژه ارائه شده.

در ثانی، برای هندل کردن باس، شما لازمه مطابق Datasheet آی.سی FT2232H با رویت وضعیت سیگنال RXF# و TXE# در هر لحظه اقدام مقتضی را انجام بدید که در این پروژه نمونه این کار توسط ماژول afifo پیاده سازی شده و شما برای فرستادن دیتا به سمت PC کافیه در FIFOی TX بنویسید و برای دریافت داده های ارسالی از سمت PC کافیه از FIFO ی RX بخونید و شما میتونید عینا همین ماژول را بردارید و توی پروژه خودتون استفاده کنید.

ممنون میشم ادامه بحث را در این تاپیک در انجمن ها ادامه بدیم:

ارتباط USB بین FPGA و کامپیوتر با سرعت ۸ MB/s با استفاده از FT2232H در حالت Async FIFO

سلام

این به طور مستقیم به ISE ارتباط برقرار نمیکنه ؟

امکان دیباگ کردن مثل زایلینکس کابل چطور؟

با سلام

نخیر این مود تنها برای انتقال دیتا می باشد.