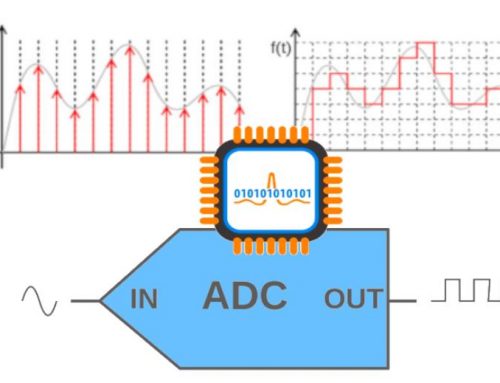

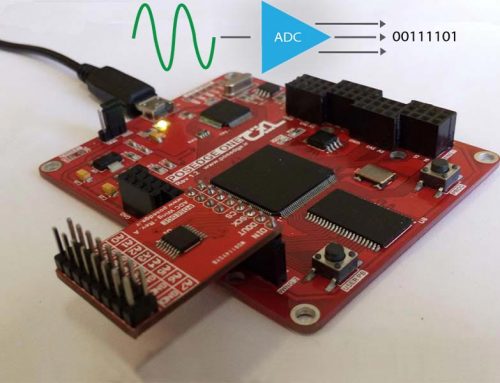

در این سری آموزشهای ویدئوی که توسط مهندس “سیاوش ادیب” از گروه MicroLab تهیه شده است، تلاش شده است از صفر تا صد انتقال دادههای یک سیستم به سیستم دیگری بصورت سریال توسط تراشهی Xilinx SPARTAN-6 FPGA آموزش داده شود. در این پروژه قرار است دادههای مبدل آنالوگ به دیجیتال ADC128S102 بصورت سریال به سیستم دیگری (PC) انتقال داده شوند، در مورد نحوه راه اندازی ADC128S102 در ویدیوهای قبلی بطور کامل بحث شده است، شما میتوانید پروژه راهاندازی مبدل آنالوگ به دیجیتال ADC128S102 را از اینجا مشاهده کنید.

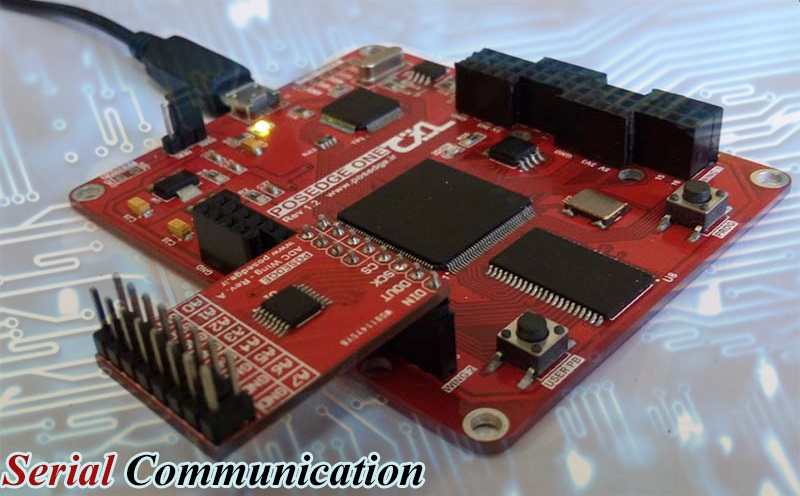

سخت افزار مورد نیاز:

بخش اول: مقدمه

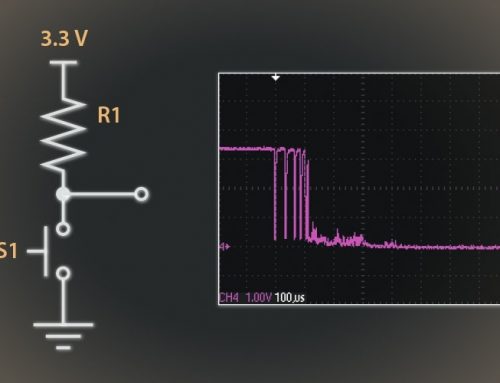

در این ویدیو ابتدا هدف و نقشه راه پروژه توضیح داده شدهاست و در مورد پارامترهای مهم سیستم که قرار است طراحی شود، از جمله مقادیر کانال های ADC، مقادیر LEDها و مقادیرسوئیچها که قرار است کامپیوتر(یا سیستم دیگری) این پارامترها را بطور دائم مانیتور کند، بحث شدهاست.

بخش دوم : بررسی ماژول PC_Communication_Center

در این ویدیو به بررسی ماژول PC_Communication_Center پرداخته می شود. ماژول PC_Communication_Center از دو ماژول PC_TX_Module و PC_RX_Module تشکیل شده است که وظیفه ماژول PC_RX_Module ، دریافت و آنالیز بستههای که حاوی دستوراتی از طرف کامپیوتر میباشد، است و همچنین پارامتری که کامپیوتر از آن درخواست کرده را به ماژول PC_TX_Module گزارش می دهد تا ماژول PC_TX_Module پارامتر مورد نظر را برای کامپیوتر ارسال کند.

ماژول PC_RX_Module نیز از دو ماژول PC_RX_Packet_Hndler و PC_Buffered_RX تشکیل شدهاست. وظیفه PC_Buffered_RX این است که یک بسته کامل ( چندین بایت که در قالب خاصی کنار هم قرار گرفتهاند) را دریافت کند و آن را در اختیار ماژول PC_RX_Packet_Hndler قرار دهد.

ماژول PC_Buffered_RX از ماژولهای زیرتشکیل شده است:

- Buffer RAM_64: مقدار بایتها را نگه می دارد.

- UART_RXاز خط سریال یک بایت را دریافت میکند و آن را به ماژول UART_RX_Buffer_Controller تحویل میدهد.

- UART_RX_Buffer_Controller : بایت دریافتی را در موقعیتهای مختلفی از خانههای حافظه Buffer RAM_64 قرار دهد.

بخش سوم : پیادهسازی ماژول Buffer RAM_64

دو نوع Ram در FPGA وجود دارد ،Block Ram و دیگری Distributed Ram است. به Ramهایی که از قبل در FPGA تعبیه شدهاند، Block Ram میگویند اما Distributed Ram، از LUTها و رجیسترها ساخته میشود و بهتر است Ramهای کوچک بصورت Distributed Ram پیادهسازی شوند زیرا این نوع Ram بر خلاف Block Ram مکان مشخصی در FPGA ندارند، Block Ramها در مکانهای خاصی از FPGA قرار دارند که در هنگام پیاده سازی باعث ایجاد محدودیتهایی میشوند. در این ویدیو Buffer RAM_64 بصورت Distributed Ram پیادهسازی میشود. بدین منظور از Distributed Memory ipcore استفاده میشود و Data Width آن برابر یک بایت یعنی 8 بیت و Depth آن نیز برابر 4 در نظر گرفته شده است و Memory type آن، simple Dual port در نظر گرفته شدهاست. Ramها میتوانند single port یا Dual port باشند. در single port نمی توان همزمان روی Ram عملیات خواندن و نوشتن را انجام داد زیرا باس آدرس مشترک است. اما این محدودیت در Dual port وجود ندارد.

بخش چهارم: پیاده سازی UART_RX_Buffer_Controller

این ماژول علاوه بر ذخیره کردن دادهها در RAM، باید بایتهای دریافتی را کنار هم بچینند و بصورت یک packet در آورده سپس آنها را تحویل ماژول PC_RX_Packet_Hndler دهد. در این بخش در مورد نحوه تشکیل packetها بحث میشود.

بخش پنجم: پیاده سازی PC_Buffered_RX

در این بخش سه ماژول Buffer RAM_64، UART_RX_Buffer_Controller و UART_RX به این ماژول اضافه می شوند.

بخش ششم: پیادهسازی PC _RX_Packet_Handler

این ماژول دارای چهار ورودی خروجی o_Command_BUS ،io_Buffered_RX، i_RST و i_CLK میباشد. خروجی o_Command_BUS در واقع حکم یک باس را دارد که بعد از اینکه packet مورد نظر، در این ماژول آنالیز شد بوسیله Command_BUS به یک ماژول دیگر (در اینجا همان ماژول tx مد نظر است) دستور اجرای فرمان مدنظر، طبق packet دریافتی داده میشود.

io_Buffered_RX هم شبیه همان io_Buffered_RX است که داخل ماژول PC_Buffered_RX پیادهسازی شدهاست، هست فقط کافی است که آن را داخل این ماژول کپی نموده و ورودی های آن را تبدیل به خروجی و خروجی های آن را تبدیل به ورودی نماییم. همچنین در این ویدیو پکیج نویسی با زبان VHDL نیز آموزش داده شده است.

بخش هفتم: ادامه پیاده سازی PC _RX_Packet_Handler

در این ویدیو در مورد ساختار packetها بحث میشود. اندازه packetها برابر 10بایت در نظر گرفته شده است که:

- 4 بایت برای header

- 4 بایت برای footer

- 2 بایت نیز برای دادهها

اختصاص داده شدهاست. در این بخش از یک state machine برای بررسی packet دریافتی و چک کردن header ،footer واستخراج داده های packet ، استفاده شدهاست.

بخش هشتم : ادامه پیاده سازی PC _RX_Packet_Handler

در این ویدیو هنگامیکه state machine در state_check_Header قرار دارد بحث میشود، همچنین در مورد بررسی Head بستهها نیز توضیحانی داده میشود. همچنین یک state machine دیگر برای خواندن از روی Ram نیز در نظر گرفته شدهاست. که این state machine دارای سه حالت :

- Set_Address

- Wait_for_data

- Read_data

میباشد. که ابتدا آدرس مورد نظر را قرار داده، یک state صبر نموده و سپس درstate بعدی دادهها خوانده میشوند.

بخش نهم : ادامه پیاده سازی PC _RX_Packet_Handler

در این ویدیو هنگامیکه state machine برنامه در state_check_Footer قرار دارد، توضیحاتی را ارائه میکند و نحوه بررسی Footer بستهها را آموزش میدهد.

بخش دهم: ادامه پیاده سازی PC _RX_Packet_Handler

در این ویدیو هنگامیکه state machine در state_Extract_Command قرار دارد را توضیح میدهد و نحوه استخراج Command از بسته دریافتی را بررسی میکند و در آخر کل ماژول نوشته شده، سنتز میشود و ماژول PC _RX_Packet_Handler تکمیل میگردد. در ادامه زیرماژولهای PC _RX_Packet_Handler و PC_Buffered_RX در ماژول بالادستی PC_RX_Module جایگذاری میشوند.

بخش یازدهم: پیاده سازی ماژول PC_TX_Module

این ماژول نیز از دو زیر ماژول PC _TX_Packet_Handler و PC_Buffered_TX تشکیل شدهاست. ماژولPC_Buffered_TX نیز مانند ماژول PC_Buffered_TX است و از سه زیر ماژول Buffer_RAM_64، UART_TX_Buffer_Controller و UART_TX تشکیل شدهاست. در این ویدیو نحوه پیاده سازی ماژول UART_TX_Buffer_Controller بررسی میشود.

بخش دوازدهم: ادامه پیاده سازی ماژول PC_TX_Module

در این بخش سه ماژول Buffer_RAM_64، UART_TX_Buffer_Controller و UART_TX در ماژول بالادستیPC_Buffered_TX فراخوانی میشوند. بعد از اتمام ماژول PC_Buffered_TX، ماژول PC _TX_Packet_Handler پیاده سازی میشود. برای پیاده سازی این ماژول نیز از state machine استفاده شده است. بنابراین 7 حالت مختلف برای این state machine در نظر گرفته شده است.

بخش سیزدهم: ادامه پیاده سازی ماژول PC_TX_Module

در این ویدیو در مورد حالت اول که State_IDLE می باشد بحث میشود. در این حالت باید برنامه منتظر دریافت یک Command جدید شود و هنگامیکه آن را دریافت نمود، آن را بررسی نموده تا بتواند state بعدی را انتخاب کند.

بخش چهاردهم: ادامه پیاده سازی ماژول PC_TX_Module

در این ویدیو در مورد State_ Send_Switch_States و State_ Send_ADC_Channel_Value بحث می شود. در State_ Send_ADC_Channel_Value دو بایت داده بعنوان جواب فرستاده میشود و در این دو بایت باید یکی از مقادیر ADC_Channel ها فرستاده شوند که هر کدام از کانال ها در این پروژه 12 بیت هستند همچنین باید مشخص کنیم که مقادیر کدام از کانال ها فرستاده می شوند. از طرفی تعداد کانالها برابر 8 است.

بخش پانزدهم: ادامه پیاده سازی ماژول PC_TX_Module

در این ویدیو در مورد نحوه پیادهسازی state_send_Diag، state_Send_Packet_Error و state_Cleanup بحث میشود.

بخش شانزدهم: ادامه پیاده سازی ماژول PC_TX_Module

در این ویدیو PC_TX_Packet_Handlerو PC_Buffered_TX به ماژول بالادستی PC_TX_Module اضافه میشوند.

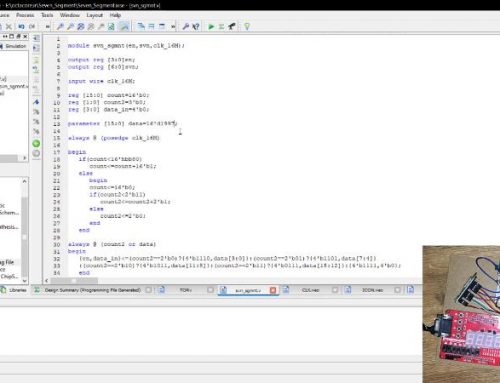

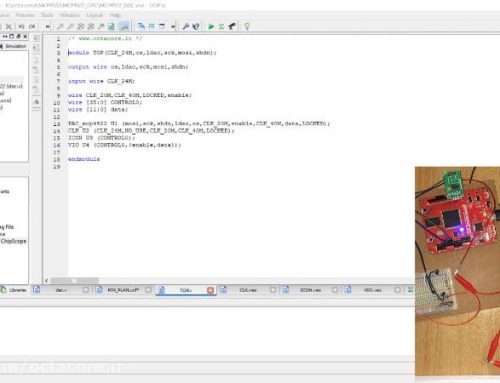

بخش هفدهم : پیاده سازی ماژول Communication_Center

در این ویدیو یک ماژول به نام Communication_Center ایجاد می شود و ماژولهای PC_TX_Module و PC_RX_Module به آن اضافه میشود. سپس ماژول Communication_Center به Top_Module اضافه می شود.

بخش هجدهم: تست عملی

برای تست و ارتباط گرفتن با برد پازج، یک GUI ساده نوشته شده است و در این ویدیو نحوه تست برنامه را میتوانید مشاهده کنید.

بخش نوزدهم: تعریف Snippet

در این ویدیو ، snippest های سفارشی در ویرایشگر sublime text آموزش داده می شود.

این مورد رو هم در نظر داشته باشید که حتماً اون سطری که Scope این Snippet شما رو مشخص می کند را لحاظ کنید. چون در غیر این صورت، Snippet شما تو همه Syntax های Sublime اضافه می شود و این مطلوب نخواهد بود. برای مثال در اینجا این سطر نوشته شده است که این Snippet که برای Record در VHDL نوشته شده، فقط در فایل هایی با VHDL Syntax لحاظ بشود.

دانلود فایل های پروژه:

مطالب عالی هستن. اگه امکانش هست فایل دانلود ویدئوها را هم قرار بدید.

با تشکر.

سلام

با کلیک روی آیکن چرخ دنده در نوار پایین هر ویدئو میتونید دانلودش کنید.

موفق باشید.

چرخ دنده نداره

هر ویدئو رو که اجرا کنید در کنار فریم نمایش ویدئو یک چرخ دنده وجود داره که با کلیک روی اون و انتخاب گزینه دانلود میتونید ویدئوی آموزشی رو دانلود کنید

سلام خسته نباشید.

میخواستم بپرسم این برنامه تحت ویندوز برای ارتباط UART را با چه زبانی نوشته اید ؟

امکان دارد فایل سورس آن برنامه را هم برای دانلود قرار دهید؟

با سلام

لینک حاوی نرم افزار سمت PC همراه با سورس آن اضافه شد.

موفق باشید.

ممنون متفاوت از همه