مقدمه

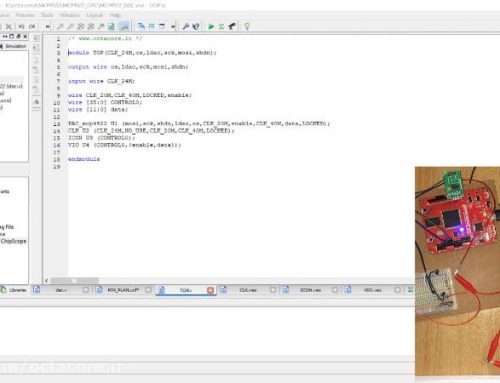

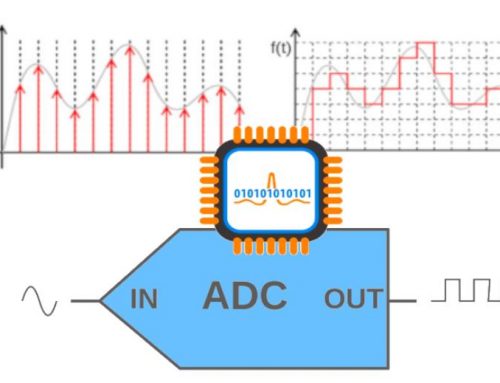

در قسمت اول این آموزش به معرفی بال ADC و روش های پیاده سازی آن روی FPGA پرداختیم. در این قسمت می خواهیم با استفاده از واسط SPI که خودمون طراحی کردیم با تراشه ADC128S102 ارتباط برقرار کنیم و نمونه داده های دیجیتال شده کانال های مختلف این تراشه را داخل FPGA خوانده و در این پروژه داده ها را به صورت یک PLOT در متلب نشان دهیم.

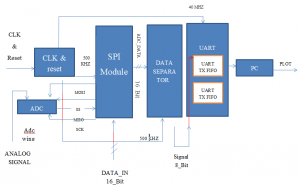

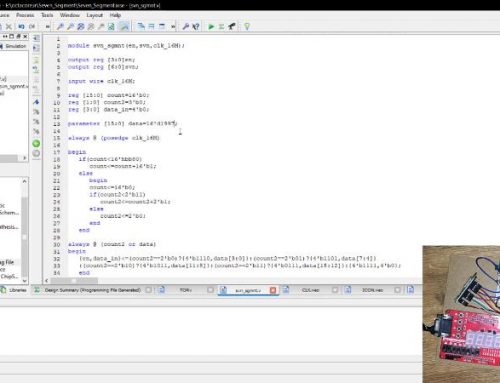

در شکل زیر بلوک دیاگرام کلی این پروژه را مشاهده می کنید. طراحی انجام شده به صورت HDL کامل و به زبان Verilog نوشته شده است و سورس آن و پروژه قابل اجرا روی برد پازج به همراه بال ADC را می توانید در انتهای این آموزش دانلود کنید.

در ادامه به بررسی هریک از این واحد ها می پردازیم.

واحد کلاک و ریست

این بلوک وظیفه دارد کلاک ورودی برد پازج که برابر ۲۴ MHZ هست را به ۱ MHzو 40 MHZ و 24 MHZ تبدیل کند تا سایر بخش های مدار از آن استفاده کنند. طبق دیاتشیت تراشهADC128S102، می توان حداکثر کلاک پایه SCKواحد SPI برابر ۱۶ MHZ باشد ولی در این طراحی ما کلاک سیستم را برابر ۱ MHz در نظر گرفته ایم.

واحد SPI

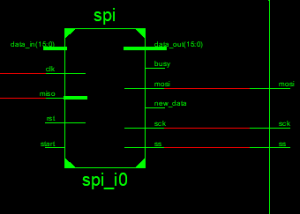

در این طراحی واحد SPI به طور پیوسته درحال خواندن ADC می باشد و کانال مورد نظر برای دریافت را از طریق ورودی ADC Channel انتخاب می کند. ما در این پروژه کانال را به طور دستی کانال شماره 0 قرار داده ایم.

در تنظیمات این بلوک پارامتری به اسم CLK_DIV وجود دارد که در واقع نشان می دهد کلاک SPI چه تقسیمی از کلاک سیستم باشد. حداقل مقدار این پارامتر برابر ۲ است و با توجه به کلاک ۱KHZ طراحی ما ، کلاک SPI برابر 0.5KHZ خواهد شد و با توجه به طول 12 بیتی ارتباط SPI حداکثر نرخ نمونه برداری در این طراحی برابر 512Hz/12= 42.66Hz خواهد بود.

اگر بخواهیم حداکثر نرخ نمونه برداری را داشته باشیم بنابراین کلاک SPI باید برابر ۱۶MHz باشد و با توجه به این که حداقل کلاک سیستم باید ۲ برابر کلاک SPI باشد بنابراین اگر کلاک سیستم برابر ۳۲MHZ باشد و مقسم کلاک برابر ۲ باشد حداکثر نرخ نمونه برداری را خواهیم داشت که برابر ۱MSPS خواهد بود.

خروجی واحد SPI به صورت یک داده ۱۶ بیتی است که با توجه به اینکه تراشه ADC128S102 نمونه های آن ۱۲ بیتی می باشد تنها ۱۲ بیت از ۱۶ بیت خورجی SPI مورد نظر است.

این واحد دارای سیگنال start است که در این طراحی به مقدار منطقی ۱ وصل شده و بنابراین همیشه این واحد فعال میباشد.

سیگنال busy هم نشان می دهد که واحد SPI در حین ارسال می باشد و سیگنال new_data نشان می دهد که ارسال به اتمام رسیده و داده ی جدیدی دریافت شده است.

ورودی data_in در واقع برای مشخص کردن داده ارسالی به بال ADC می باشد و با توجه به دیتاشیت تراشه ADC128S102 برای تعیین کانال تنها ۳ بیت از ۱۶ بیت ارسالی قابل استفاده است که این ۳ بیت مشخص کننده کانال هست که قصد داریم از آن مقدار آنالوگ را بخوانیم. برای مشخص کردن کانال در کد برنامه به صورت زیر عمل می کنیم.

.data_in({2’b00, ~channel_address, 11’b00000000000})

واحد ارسال سریال

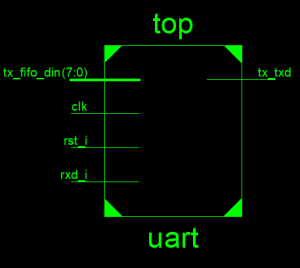

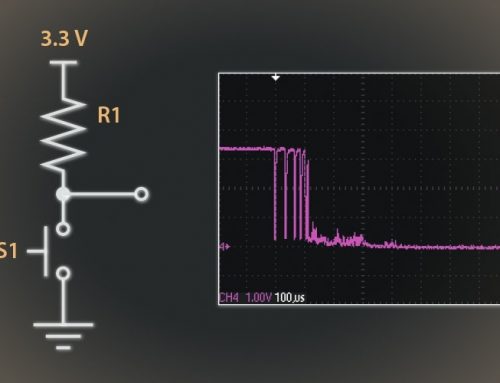

به منظور ارسال اطلاعات دریافت شده از ماژول ADC از طریق FPGA به سمت نرم افزار MATLAB از پروتکل ارتباط سریال UART استفاده شده است.

این پروتکل که در سایت پازج کدهای آماده ی آن موجود می باشد، به صورت دستی قابل تنطیم می باشد. به طوری که کافیست مقدار BAUDRATE را تنها با تغییر یک پارامتر تغییر داد.

در این ماژول فرکانس لازم MHZ40 می باشد و با توجه به این که فرکانس برد پازج 24 MHZ می باشد به کمک DCM CORE این فرکانس را ساخته و در اختیار UART قرار می دهیم.

با توجه به پروتکل UART درمیابیم که سیگنال ورودی این ماژول سیگنالی 8 بیتی می باشد ولی خروجی ADC 12 بیتی است. بنابراین مجبوریم هر دیتا را به صورت دو دیتا 8 بیتی تفکیک کنیم. البته باید توجه داشت که دیتای خروجی ADC، دوازده بیتی می باشد پس 8 بیت دوم سیگنال 4 بیت پر ارزش صفر دارد.

پس از این که دیتا 8 بیتی دریافت شد ماژول UART شروع به ارسال دیتا به صورت سریال می کند. دیتا در این پروژه با BAUDRATE با انداره ی 115200 ارسال خواهد شد. این مقدار با توجه به محاسبات مناسب برای دریافت و ارسال انتخب شده است. با توجه به اینکه در این پروژه مقدار CLK_DIV برابر 2 میباشد فرکانس SPI برابر 500 HZ خواهد شد. این مقدار مبین این است که نرخ نمونه برداری SPI 42.6=12/512 SPS است.

باید به این نکته توجه کرد که فرکانس UART 115200 می باشد، پس سرعت ارسال آن 7.2=115200KSPS/16 خواهد بود که این نرخ از نرخ SPI کمتر خواهد بود.

با توجه به آن چه تا به حال گفته شد، هر سمپل خروجی SPI 16 بیت و هر سمپل UART 8 بیت است. پس لازم است برای جلوگیری از اختلال در دریافت از سینک ورد استفاده می کنیم. به این صورت که هر 12 بیت را به 2 داده 6 بیتی تقسیم می کنیم وهر 6 بیت به همراه دو بیت پرارزش صفر یا یک فرستاده می شود. هر 4 دیتای 6 بیتی به همراه 2 بیت سینک ورد تشکیل یک پکت 24 بیتی می دهند که به صورت 8 بیتی ارسال می شوند.

عملیات تفکیک و جداسازی داده ها در متلب انجام می شود و سپس هر دو 6 بیت پشت سر هم که به درستی دریافت می شوند دوباره به صورت دیتا 12 بیتی درمی آیند و ذخیره می شوند.

واحد MATLAB

ابتدا لازم است که تنظیمات متلب را برای دریافت سریال داده ها به صورت دستی تنظیم کنیم.

BAUDRATE را 115200 ، PARITY:NONE ، DATABITS:8 ، STOPBIT: ، TIMEOUT:10 .

اما دریافت دیتا:

متلب توان دریافت سریال داده ها را دارد. با استفاده از دستور fopen+fread متلب یک سمبل 8 بیتی را در اختیار ما قرار

میدهد.

packet_in1=fread(s,1,’char’); %read 1 byte to a, make sure that the input buffer size is > the no of bytes you read.

باید توجه داشت یک سمبل کامل که از ماژول ADC دریافت شد 12 بیتی است. پس برای استخراج کامل آن باید دو سمبل 8 بیتی را کنار هم قرار داد. این عمل در نرم افزار متلب با تبدیل دیتاهای 8 بیتی به دیتای Bitstream انجام میشود. متلب به راحتی می تواند دو دیتای 8 بیتی را به هم وصل کند.

پس از دریافت کامل پکت 24بیتی دو دیتای 12 بیتی را استخراج کرده و هر سمبل کامل را در یک آرایه نگهداری میکنیم.

x=data1*6

y=data2-128

w=data3-128

z=w*64

t=data4-128

data(i)=x+y

i=i+1

data(i)=z+t

i=i+1

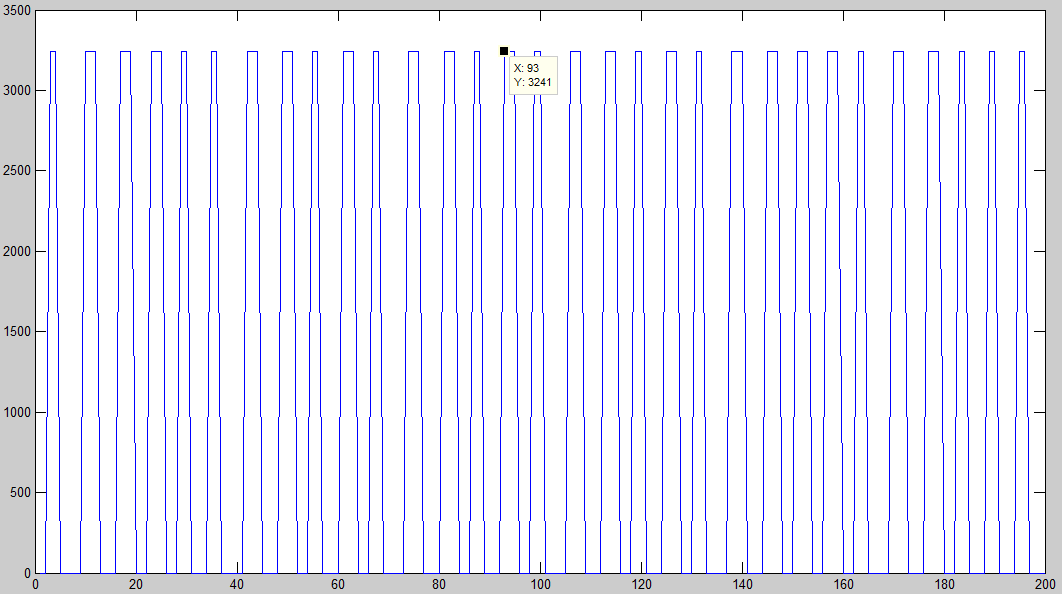

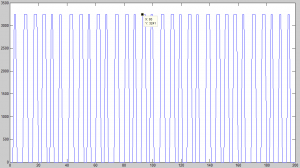

پس از پر شدن آرایه با دستورPLOT با توجه به تعداد سمبل دریافتی نمودار سیگنال اولیه نمایش داده می شود.

axis(

فایل بارگذاری شده خراب است

سلام.

چک شد. مشکلی نداشت.

سلام.میشه توضیح بدید که داده های که تو fpga کد شدند چطوری تو متلب خونده میشن؟ از متن برنامه چیزی نفهمیدم.الگوریتمشو بی زحمت توضیح بدید خیلی خوبه…و چطور می فهمیم داده بدون خطا اومدن؟

سلام. با آگاهی از روش کد کردن هر بایت داده مشخص است که دو بیت پایانی برای سینک شدن گیرنده و فرستنده است. با توجه به اینکه طبق کد بایت اول دوبیت پر ارزش صفر دارد پس این بایت فقط حاوی اطلاعات است. در سه بایت بعدی بیت پر ارزش یک و بیت پر ارزش دوم صفر است. پس کافیست این سه بایت منهای ۱۲۸ شده تا بیت پر ارزش خنثی شوند.

حال هر ۴ بایت دریافتی که بایت اول آنها سینک ورد صفر و ۳ بایت دوم سینک ورد ۱ دارند قابل قبول خواهند بود و پس از عملیات فوق دو ۶ بیت در کنار هم قرار می گیرند. اینکار با ضرب بایت ثانویه در دو به توان ۶ و جمع با بایت اولیه انجام میشود. مشخص است که این ضرب در دنیای صفر و یک معادل ۶ بار شیفت به چپ است.

خیلی متشکرم.خدایت خیر دهاد.

و یک سوال دیگه اینکه در ماژول manager_data چرا ۴ تا ۶ بیت کد میشه؟دلیل ویژه ای دارید که دو تا دوازده بیت رو سمت متلب می فرستید؟

به دو دلیل این روش بهتر است.

با توجه به امکان loss شدن اطلاعات اگر یک ۱۲ بیت در قالب ۲ بایت ارسال شود ممکن است با از دست رفتن یک بایت متلب مبدا زمانی خود را گم کند. اما با این روش اگر متلب سه بایت پشت سر هم با این روش کدینگ مشاهده نکند آن ۴ بایت را دور میریزد.

و همچنین این روش باعث میشود بتوان چند دستگاه (تا سقف ۳۲) را به کمک دو بیت پایانی این بایت از هم تفکیک و شناسایی کرد.

سلام.تو ماژول manager چرا کلاک یک مگا یکدفعه تقسیم بر ۴۴ میشه و بعد خروجی ۸ بیتی ماژول به فیفو ای داده میشه که کلاکش ۴۰ مگه!!

نحوه ی توزیع کلاک ها و دلیلش رو توضیح بدید ممنون میشم…مثلا چرا ماژول یوآرت ۴۰ مگ کلاکشه؟

سلام ممکنه طریقه تولید سیگنالهای مربعی و دندانه اره ای و مثلثی و سینوسی با فرکانس قابل تنظیم در fpga رو هم توضیح بدید .

ممنون