در پست قبلی به معرفی محیط توسعهی محبوب DesignLab پرداختیم و بطور خلاصه با برخی از ویژگیها و قابلیتهای آن آشنا شدیم. در ادامهی بحث قبل، در این پست قصد دارم تا مراحل نصب نرمافزار و شروع اولین پروژه در محیط DesignLab و اجرای آن روی برد پازج-1 را بصورت گام به گام تشریح کنم. سخت افزار لازم برای انجام این پروژه، برد پازج-1 و بال LED و کلید است.

گام اول: نصب DesignLab

برای شروع آخرین نسخه نرم افزار DesignLab را از لینک روبرو دریافت و نصب کنید (دانلود DesignLab)

(در زمان نگارش این نوشته آخرین نسخه نرمافزار، نسخهی 1.0.8 است).

در هنگام نصب سعی کنید حتی المقدور برنامه را در مسیری نصب کنید که آدرس آن حاوی فاصله و یا کاراکترهای خاص نباشد.

گام دوم: نصب patch پازج

اکنون بایستی patch مخصوص اضافه کردن برد پازج-1 را روی Designlab نصب کنیم. با این کار برد پازج-1 به لیست بردهای موجود در این نرم افزار اضافه خواهد شد.بدین منظور

- ابتدا آخرین نسخه پچ را از لینک مقابل دانلود کنید: (دانلود Patch – آپدیت 97/09/30 :حل مشکل بارگذاری برنامه (sketch) روی فلش، حل مشکل flexpinها و اضافه کردن مثال Encoder_PWM)

- فایل دانلود شده را که یک فایل فشرده به فرمت Zip میباشد درون پوشهی محل نصب DesignLab اکسترکت نمایید و بر روی فایلهای قبلی overwrite نمایید.

نکته: این patch همواره در حال بروزرسانی است و به مرور تکمیل میشود. اخبار مربوط به تکمیل این patch از طریق کانال تلگرامی پازج اطلاع رسانی میشود.

گام سوم: اجرای اولین پروژه در محیط DesignLab.

انتخاب برد:

اکنون شما آماده هستید تا اولین پروژه خود با DesignLab را روی برد پازج-1 اجرا کنید. بدین منظور DesignLab را اجرا کنید و از منوی Tools -> Board -> Papilio FPGA Boards گزینهی Posedge One FPGA – Zpuinoرا انتخاب نمایید.

اجرای پروژه نمونه

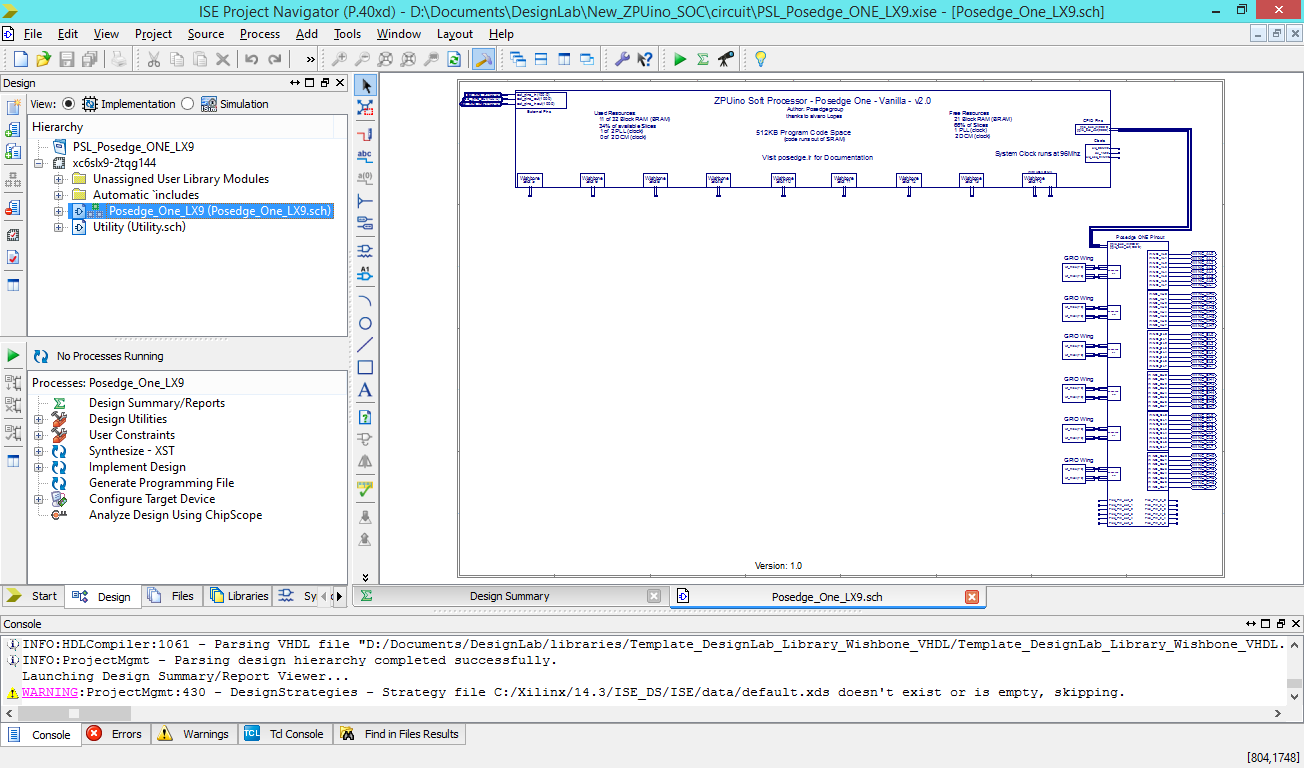

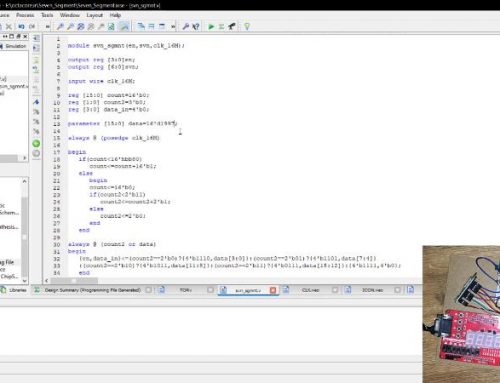

اکنون از منوی File -> Examples پروژهی نمونهی Papilio_Quickstart را انتخاب نمایید و صبر کنید تا پروژهی مذکور در پنجرهی جدید باز شود. سپس از نوار ابزار بالای نرمافزار روی آیکن ![]() (Edit Circuit) کلیک کنید تا بخش سخت افزاری مربوط به این پروژه در نرم افزار ISE باز شود. توجه داشته باشید که جهت ادامه ی کار، نرم افزار از شما میخواهد تا پروژه را در محلی روی کامپیوترتان ذخیره کنید. مسیر پیش فرض پیشنهادی نرم افزار را بپذیرید و صبر کنید تا ISE باز شود.

(Edit Circuit) کلیک کنید تا بخش سخت افزاری مربوط به این پروژه در نرم افزار ISE باز شود. توجه داشته باشید که جهت ادامه ی کار، نرم افزار از شما میخواهد تا پروژه را در محلی روی کامپیوترتان ذخیره کنید. مسیر پیش فرض پیشنهادی نرم افزار را بپذیرید و صبر کنید تا ISE باز شود.

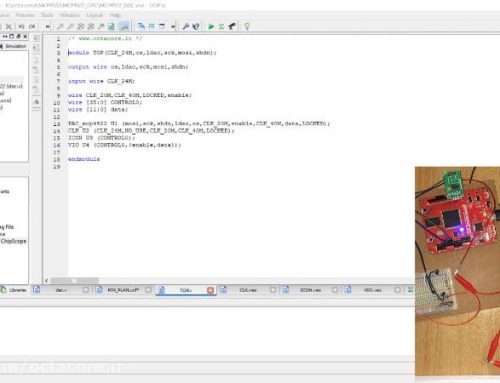

همانطور که در تصویر ملاحظه میکنید، Top module این پروژه در محیط شماتیک نرم افزار ISE رسم شده است. سخت افزار این پروژه متشکل از یک هستهی ZPUino (بخوانید زی.پی.یو.اینو!)سفارشی شده برای برد پازج-1 است که شامل حداقل سخت افزار لازم جهت عملکرد ZPUino است که متشکل از واحدهای UART (متصل به مبدل USB به سریال روی برد)، SPI (متصل به حافظهی Flash روی برد)، کنترلر SRAM (متصل به SRAM روی برد) و GPIO (متصل به کانکتورهای روی برد) میباشد. در آینده خواهیم دید که چگونه میتوانیم به سادگی و با استفاده از کتابخانهی پربار Designlab، رنج وسیعی از پریفرالها را به طرح سخت افزاری خود اضافه کنیم و یا حتی از کورهای رایگان سایت opencores.org (که غالبا دارای اینترفیس wishbone هستند) استفاده کنیم.

در هر صورت، برای این آموزش لازم نیست تغییر خاصی در طرح سخت افزاری اعمال کنید و صرفا کافی است با دابل کلیک روی گزینهی Generate Programming File، صبر کنید تا مراحل ساخت فایل پیکره بندی سخت افزار به اتمام رسد. اکنون به سادگی نرم افزار ISE را ببندید و به DesignLab برگردید!

آپلود فایل پیکره بندی سخت افزار (Upload Circuit)

اکنون قصدا داریم فایل پیکره بندی سخت افزار (یا همان Circuit) ساخته شده در مرحلهی قبل را روی FPGA بارگذاری کنیم. برای این کار کافی است بر روی آیکن ![]() (Load Circuit) در نوار ابزار بالای DesignLab کلیک کنید تا این کار به سادگی هر چه تمامتر انجام شود!

(Load Circuit) در نوار ابزار بالای DesignLab کلیک کنید تا این کار به سادگی هر چه تمامتر انجام شود!

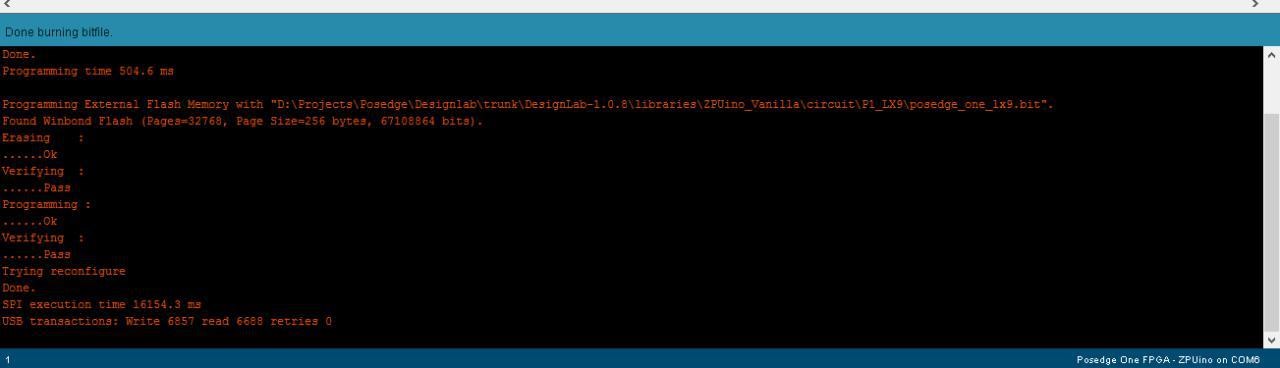

پس از اتمام موفقیت آمیز این مرحله پیغامی شبیه به تصویر زیر در قسمت پایینی محیط DesignLab نمایش داده میشود و چراغ آبی رنگ روی برد (DONE LED) یک بار خاموش و روشن میشود که نشان از اجرای موفقیت آمیز این مرحله دارد. بهتر است بدانید که این فایل بر روی حافظهی Flash روی برد بارگذاری میشود و با خاموش شدن برد از بین نمیرود.

اکنون یک ZPUino ی 32 بیتی با فرکانس 96 مگاهرتز روی FPGA آمادهی دریافت و اجرای اوامر شما است!

بررسی و اصلاح Sketch

حالا نوبت به آپلود قسمت نرم افزاری طرح (یا همان sketch در ادبیات آردوینو!) روی برد است. قبل از انجام این کار بد نیست نگاهی به کد بیندازیم. با نگاهی به کد مشخص میشود که چه کاری قرار است انجام شود:

این برنامه متشکل از دو قسمت است:

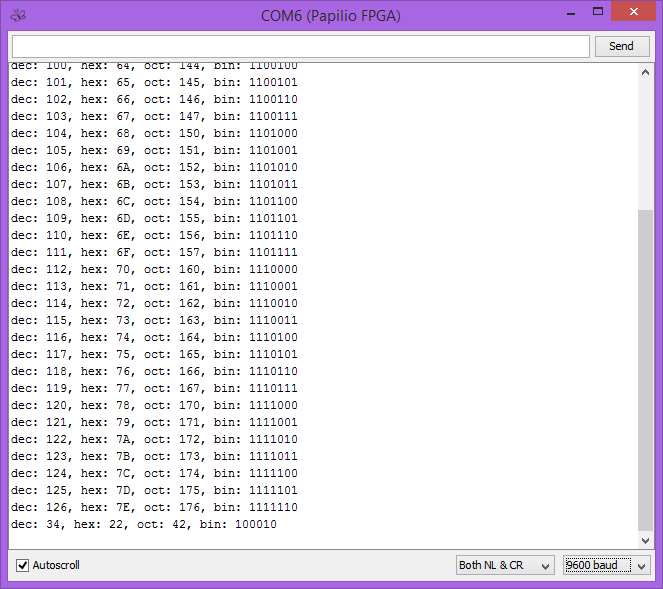

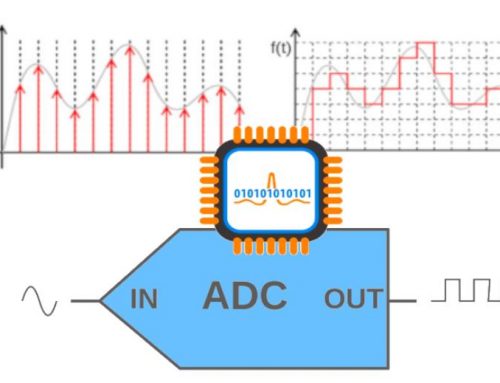

قسمت اول مربوط به ایجاد یک ارتباط سریال با نرخ 9600 و ارسال یک متن نمونه (در این مورد جدول اسکی) است.

در قسمت دیگری از این برنامه پینهای GPIO ی موجود روی کانکتورها تست میشوند. همانطور که میدانید برد پازج-1 دارای 48 پین ورودی/خروجی است که روی کانکتورها آورده شدهاند. در نرم افزار DesignLab به منظور دسترسی به این پینها و خواندن/نوشتن آنها به هر کدام از آنها شمارهای بین 0 تا 47 اختصاص یافته است که در جدول زیر میتوانید نحوهی اختصاص این شمارهها را ملاحظه نمایید.

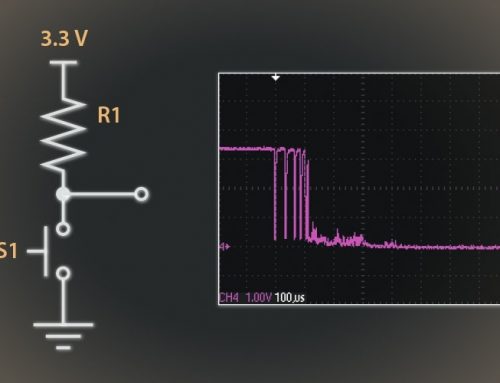

در این برنامهی نمونه، پین های با شماره زوج (2,0,…,46) در وضعیت خروجی تنظیم شدهاند و در حالت چشمک زن قرار گرفتهاند. پینهای با شماره فرد (3,1,…,47) نیز در حالت ورودی تنظیم شده اند. با فشردن هر کلید، LED کناری آن از چشمک زدن باز میایستد و روشن میماند. در این برنامه فرض بر این بود که کلیدها بصورت Active-High هستند، یعنی بصورت پیش فرض مقدارشان 0 است با با فشردن آنها مقدارشان به 1 تغییر مییابد. اما از آنجا که قصد ما اجرای این مثال روی برد پازج-1 با استفاده از بال LED و کلید است، و نوع طراحی کلیدها در این بال بصورت Active-Low است (یعنی بصورت پیش فرض مقدارشان 1 است و با فشردن آنها مقدارشان به 0 تغییر پیدا میکند)، لازم است اصلاح کوچکی در کد انجام دهیم تا نتیجه مطابق انتظار شود. بدین منظور کافی است تا عبارت

if (buttonState == HIGH) {

در قسمت انتهایی برنامه را به صورت زیر تغییر دهیم:

if (buttonState == LOW) {

با این توضیحات به سراغ آپلود کد روی برد میرویم.

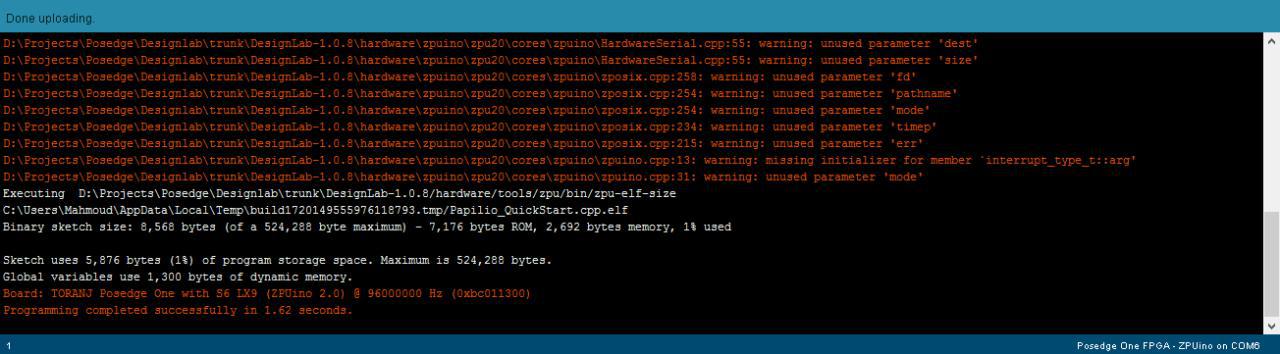

آپلود Sketch

برای تست این قسمت از برنامه شما نیاز به یک بال LED و کلید دارید. بال LED و کلید را در یکی از 6 مکان موجود روی کانکتورهای برد قرار دهید و با کلیک بر روی آیکن ![]() (Upload) در نوار ابزار بالای نرمافزار کد نرمافزاری خود را روی برد آپلود کنید. در صورتی که این مرحله ازعملیات نیز موفقیت آمیز باشد، پیغامی شبیه تصویر زیر در قسمت پایین نرم افزار نمایش داده خواهد شد و چراغ LED آبی رنگ روی برد (DONE) نیز یک بار خاموش و روشن میشود.

(Upload) در نوار ابزار بالای نرمافزار کد نرمافزاری خود را روی برد آپلود کنید. در صورتی که این مرحله ازعملیات نیز موفقیت آمیز باشد، پیغامی شبیه تصویر زیر در قسمت پایین نرم افزار نمایش داده خواهد شد و چراغ LED آبی رنگ روی برد (DONE) نیز یک بار خاموش و روشن میشود.

در پستهای آتی سعی خواهیم کرد با انجام پروژههای جذابتر و کاربردیتر، با قابلیتهای این IDE زیبا و دوستداشتنی بیشتر آشنا شویم.

آموزش ویدئویی نصب و اجرای اولین پروژه در DesignLab (بروز رسانی: 8 فروردین 96)

در ویدئوی آموزشی زیر کلیهی مراحل ذکر شده در فوق، بصورت ویدئویی و همراه با جزئیات بیشتر توسط دوست عزیزمان آقای چنگانی آموزش داده میشود. در انتهای این ویدئوی آموزشی، یک بازی ویدئویی قدیمی بعنوان پروژه نمونه با استفاده از بال VGA 12 بیتی روی مانیتور نمایش داده میشود. به لطف ZPUino و کتابخانههای پربار آن، خواهید دید که چگونه این کار سادهتر از هر زمان دیگری قابل اجرا است! تماشای این ویدئوی جذاب را از دست ندهید.

امیدوارم این نوشته مورد توجه شما قرار گرفته باشد. در صورتی که از این پست خوشتان آمده است لطفا از طریق منوی شبکه اجتماعی پایین همین پست، آن را با سایر دوستانتان در شبکههای اجتماعی به اشتراک بگذارید. از توجه شما سپاسگذارم.

سلام

مراحلی که گفتید را انجام دادم . مرحله آپلود فایل پیکربندی انجام میشه.

اما مرحله بعدی پیفام عدم اتصال را می دهد.

Could not contact ZPUino embedded programmer.

The more common reasons for this are:

a) You are not specifying the correct port. The port currently selected is ‘COM7’

b) The board FPGA is not programmed with a valid ZPUino bitfile.

c) The board is properly not powered.

Please review all of above, if problem persists please contact support.

سلام

مطمئن هستید که مرحلهی قبل به درستی انجام شده است؟

پیشنهاد میکنم یک بار Flash را بطور کامل Erase کنید (در Impact یا miniSProg) و دوباره فایل پیکره بندی را روی برد بریزید. چراغ آبی رنگ DONE را چک کنید که حتما روشن باشد.

همچنین مجددا چک نمایید که پورت سریال را به درستی انتخاب کرده باشید.

سلام

بله .مرحله اول انجام میشه پیغام :

Using built-in device list

JTAG chainpos: 0 Device IDCODE = 0x24001093 Desc: XC6SLX9

Uploading “bscan_spi_lx9_qfp144.bit”. DNA is 0x39d319898a2cd8ff

Done.

Programming time 93.8 ms

Programming External Flash Memory with “D:\Users\ISTA\Documents\DesignLab\Papilio_QuickStart\circuit\P1_LX9\posedge_one_lx9.bit”.

Found Winbond Flash (Pages=32768, Page Size=256 bytes, 67108864 bits).

Erasing :

……Ok

Verifying :

……Pass

Programming :

……Ok

Verifying :

……Pass

Trying reconfigure

Done.

SPI execution time 28580.5 ms

USB transactions: Write 6855 read 6686 retries 0

مربوط به مرحله اول.

با امپکت هم Erase کردم.فرق نکرد.

برد من Rev 1.2 هست

روی برد تغییری اعمال نکردید؟ مثلا کریستالش را عوض نکردین؟

سلام

نه تغییر ندادم .اما مد FT2232 در حالت Async FIFO هست

مربوط میشه؟

اگر بله چطور به حالت پیش فرض برگردونم؟

بله. قطعا مربوط به همین میشه. چون کانال ارتباطی برای پروگرام کردن sketch روی برد، پورت سریال هست.

برای برگرداندن مود به حالت UART از همان برنامه ftdi_change_mode استفاده کنید:

https://posedge.ir/2015/12/14/8mbps_fpga_usb_interface_ft2232_async_fifo/

سلام

ببخشید منظورم کانال دوم بود نه کانال پروگرامر.

من از ISE به راحتی از پروگرامر برای کارهای خودم استفاده میکنم

اتفاقا منظور بنده هم همون کانال دوم هست. کانال اول که به JTAG وصله برای پروگرام کردن فایل Bit در مرحلهی Load Circuit استفاده میشه که در مورد شما به درستی انجام میشه.

اما در مرحلهی Load کردن Sketch از کانال دوم (کانال B) در حالت UART استفاده میشه که چون در برد شما این کانال روی حالت FIFO تنظیم شده، ارتباط به درستی برقرار نمیشه.

سلام

تشکر .مشکل همین بود

سلام

بعد از پروگرم کردن سخت افزار با فایل bit در زمان ریختن فایل کامپایل شده elf پیغام زیر نمایش داده می شود و بارگذاری متوقف می شود

Board: TORANJ Posedge One with S6 LX9 (ZPUino 2.0) @ 96000000 Hz (0xbc011300)

Unknown flash type, exiting

سلام

آپدیت ۹۷/۰۹/۲۰: در نسخهی جدید patch این مشکل برطرف شده است!

متاسفانه این مشکل روی برخی فلشهامون وجود داره و هنوز توجیهی براش پیدا نکردم…عجالتا میتونید به روش زیر فایل برنامه را مستقیما روی خود FPGA لود کنید:

در مسیر نصب DesignLab به مسیر “\hardware\zpuino\zpu20″ رفته و فایل platform.txt را باز کنید.

عبارت

tools.zpuinoprogrammer.upload.pattern=”{path}/{cmd}” -s {upload.speed} -R {upload.verbose} {upload.memory} -d {serial.port} -b “{build.path}/{build.project_name}.bin” {upload.smallfs}

را با عبارت زیر جایگزین کنید:

tools.zpuinoprogrammer.upload.pattern=”{path}/{cmd}” -U -s {upload.speed} -R {upload.verbose} {upload.memory} -d {serial.port} -b “{build.path}/{build.project_name}.bin” {upload.smallfs}

و تغییرات را ذخیره کنید.

نرم افزار DesignLab را یک بار دیگر اجرا کنید. بایستی مشکل برطرف شده باشد.

سلام

لطفا نسخه fpgaprog برای لینوکس یا سورس کد آن را فراهم نمایید

با سپاس